金山PDF阅读器 0.1.0.6621免费下载,pdf文件怎么打开?

台积电研发负责人、技术研究副总经理黄汉森(Philip Wong)在本周开幕的第 31 届 HotChips 大会专题演讲中如是说。

在现场的幻灯片中,台积电甚至前瞻到了 2050 年,晶体管来到氢原子尺度,即 0.1nm。

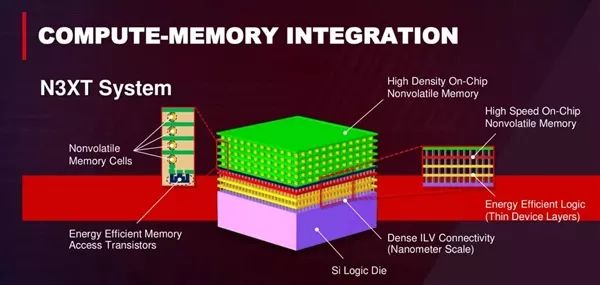

关于未来的技术路线,黄汉森认为像碳纳米管(1.2nm 尺度)、二维层状材料等可以将晶体管变得更快、更迷你;同时,相变内存(PRAM)、旋转力矩转移随机存取内存(STT-RAM)等会直接和处理器封装在一起,缩小体积,加快数据传递速度;此外还有 3D 堆叠封装技术。

黄汉森强调,社会对先进技术的需求是无止境的,他还强调,除了硬件,软件算法也需要迎头赶上。

可以做小,也可以做大。

赛灵思(Xilinx)宣布推出世界最大的 FPGA 芯片“Virtex UltraScale+ VU19P”,拥有多达 350 亿个晶体管,密度在同类产品中也是最大的,相比上代 Virtex UltraScale VU440 增大了 1.6 倍,而功耗降低了 60%。

虽然具体面积没有公布,和日前那个 1.2 万亿晶体管、46225 平方毫米、AI 计算专用的世界最大芯片不在一个数量级,但在 FPGA 的世界里,绝对是个超级庞然大物,从官方图看已经可以盖住一个马克杯的杯口。

相比之下,AMD 64 核心的二代霄龙为 320 亿个晶体管,NVIDIA GV100 核心则是 211 亿个晶体管。

VU19P FPGA 采用台积电 16nm 工艺制造(上代为 20nm),基于 ARM 架构,集成了 16 个 Cortex-A9 CPU 核心、893.8 万个系统逻辑单元、2072 个用户I/O接口、224Mb (28MB)内存,DDR4 内存带宽最高 1.5Tbps (192GB/s),80 个 28G 收发器带宽最高 4.5Tbps (576GB/s),支持 PCIe 3.0 x16、PCIe 4.0 x8、CCIX。

该芯片采用 Lidless 无顶盖封装,优化散热,可让设计者发挥最极致的性能。

这是一颗“Chip Maker's Chip”(芯片厂商的芯片),主要面向最顶级 ASIC、SoC 芯片的仿真和原型设计,以及测试、测量、计算、网络、航空、国防等应用领域。

它还支持各种复杂的新兴算法,包括人工智能、机器学习、视频处理、传感器融合等。

VU19P FPGA 将在 2020 年秋季批量供货。

此外,中微半导体公布了该公司产品的最新进展,其中等离子体刻蚀设备已在国际一线客户从 65nm 到 14nm、7nm 和 5nm 的集成电路加工制造及先进封装中有具体应用。

此外,中微半导体的 MOCVD(化学气相沉积()设备在行业领先客户的生产线上大规模投入量产,公司已成为世界排名前列、国内占领先地位的氮化镓基 LED 设备制造商。

中微半导体是一家国产半导体装备供应商,7 月底作为科创板首批公司上市。日前中微半导体发表了 2019 年上半年财报,1-6 月实现营收 8.01 亿元,同比增长 72.03%;归属于上市公司股东的净利润 3037.11 万元,与上年同期相比扭亏为盈。

中微半导体表示,今年上半年,中微公司刻蚀设备产品保持竞争优势,批量应用于国内外一线客户的集成电路加工制造。此外,公司已成功取得 5nm 逻辑电路、64 层 3D NAND 制造厂的订单。

在验证顺利的情况下,公司将紧跟客户的生产计划、量产需求有序制定生产计划。

中微半导体的主力产品就是蚀刻机,这也是半导体制造中最重要的设备之一,用来在芯片上进行微观雕刻,每个线条和深孔的加工精度都是头发丝直径的几千分之一到上万分之一,精度控制要求非常高。

中微所说的 5nm 蚀刻机进入 5nm 供应链也不让人意外,实际上该公司去年就发布了相关消息了,旗下的蚀刻机已经获得了台积电的认证,后者的 5nm 生产线上就会使用中微公司的蚀刻机。

转载请注明:谷谷点程序 » 台积电:2050年 晶体管能做到0.1nm